2023年底

2003网站太阳集团首页欢迎您

2020级本科生

周可行、陈卓毅

先后作为第一作者

在第56届微架构国际研讨会

和第71届国际固态电路大会上

发表论文

他们分别凭借高效能仿真器

和数模转换器的设计

在专业领域取得前所未有的突破

据统计

由本科生作为第一作者

在这两个国际会议上分别发表论文

在中国高校均为首次

周可行

国内本科生“第一人”

周可行仅用了两个月的时间,就给出了让会议论文评审审核们全部通过的满意答卷,成为了国内本科生在MICRO上发表论文的第一人。

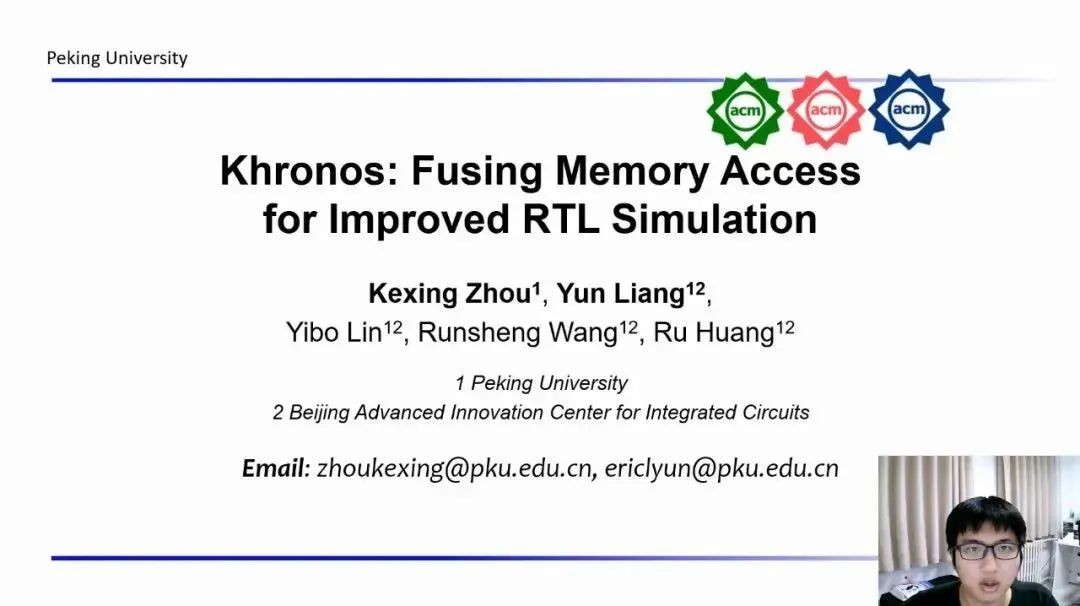

2023年10月28日到11月1日,第56届微架构国际研讨会( MICRO’56)在加拿大多伦多举行,2003网站太阳集团首页欢迎您2020级本科生周可行作为第一作者发表题为Khronos: Fusing Memory Access for Improved RTL Simulation(《融合内存访问以改进寄存器传输级仿真》)的论文,指导周可行的通讯作者是集成电路学院的研究员梁云。

作为全世界最顶级的体系结构领域的会议之一,MICRO在国内每年收录的文章不过十余篇,国内有能力向会议投稿的机构也不过十余个。相比之下,周可行仅用了两个月的时间,就给出了让会议论文评审审核们全部通过的满意答卷,成为了国内本科生在MICRO上发表论文的第一人。

寄存器传输级(RTL)仿真是芯片设计流程中重要的一个步骤。目前,软件RTL仿真器因其灵活性高、调试能力强,在RTL仿真中起到了重要作用。然而,当前最先进的仿真器也需要平均消耗45%的指令进行内存访问,消耗了大量时间,降低了整体性能。

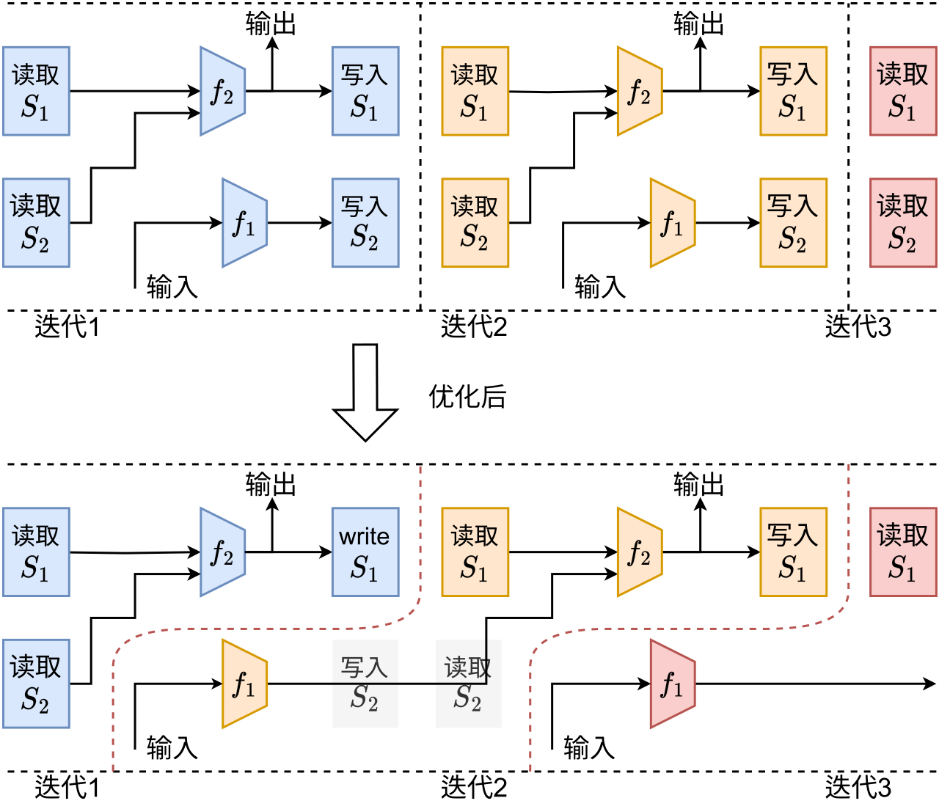

针对仿真的内存优化,周可行提出了Khronos仿真器,通过利用连续的时钟周期内内存访问的时间局部性,融合并减少了内存访问,提高了芯片验证的速度。他通过跨周期的数据依赖分析,对时钟边缘的寄存器等内存读写进行了合并优化,实现更高效的芯片仿真。与最新的仿真器相比,Khronos能够减少最高88%内存访问,提供2.0倍(最高4.2倍)的加速效能。

周可行(左)正在测试环境光对基于脉冲相机的可见光反射通信的影响

Khronos通过改变仿真顺序减少仿真过程中的内存访问

对于周可行来说,改进仿真器的想法是他“灵光乍现”的结果,但背后却是刻苦钻研的积淀和攻坚克难的决心。他对芯片硬件方面的研究非常感兴趣,从“计算机系统导论”等课程中得到启发,萌生了通过提前或者延后仿真周期提高仿真器性能的想法灵感。

周可行在MICRO会议上的线上汇报

在和导师商量后,他很快确定了自己的研究方向。从提出最初的设想,到进行形式化、建立简单的模型,再到不断优化,编译器的开发从来不是一件简单的事。周可行用了两周时间开发第一版编译器,但却失望地发现这一版结果并不能实现提高性能的设想。通过不断修改、优化方案,他又经历了近一个月的迭代才得到了令人满意的版本。

周可行坦言,在发现最初的结果不符合自己的设想初衷时,他曾感到自我怀疑,甚至一度否定自己的设想。在实验室师兄们的鼓励下,他才重拾信心,坚定自己的想法是可行的,然后不断进行实验和优化。

日复一日的实验室生活有时也让周可行感到疲惫,而他也有自己的解压方式:每到这时他就去到未名湖边散心,或者拉上实验室的三五好友下馆子、喝奶茶、谈天说地。在和大家交流过后,他重新调整好心态,又一头扎入代码中。他一步步摸索、尝试,前后经历了两个月,终于获得了令人满意的成果。

对于周可行来说,能够做出如此瞩目的工作成绩绝不是偶然。他在写代码方面有极强的能力,在很短时间内就可以写出数千行的复杂代码。科研中需要灵感,但更需要严谨和坚韧的态度,从写程序到做实验,所有的工作都由他一人承担。

“这一研究过程需要测试近十个仿真器,总共需要进行100多次实验,这些工作都由我自己来完成——因为只有自己亲历亲为才能获得更深刻的体会。”

周可行特别享受科研的过程,写代码、编程序让他感受到无穷乐趣。他谈到,尽管自己目前的工作可能无法进行应用,但是在此基础上不断改进优化,可能就会产生更快更好的仿真技术。未来,周可行将继续在北大读博,并尝试在博士期间不断突破,做出更快更好的硬件仿真器。

周可行在半导体论坛上

周可行(左)在“骑行教育”课程考试中拿到金牌

陈卓毅

对一切未知充满好奇

“未来,我希望继续研究模数转换器,在那些前人未曾涉足的领域留下自己的脚印。”

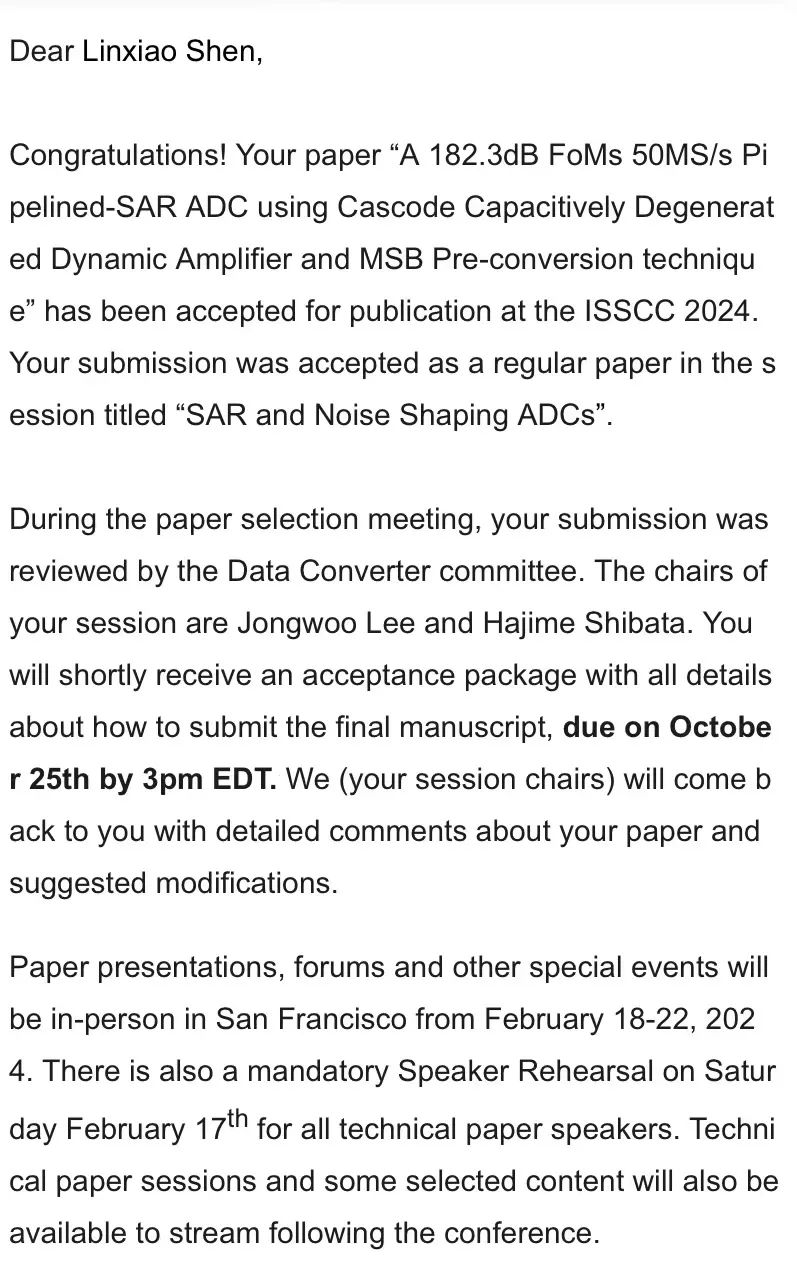

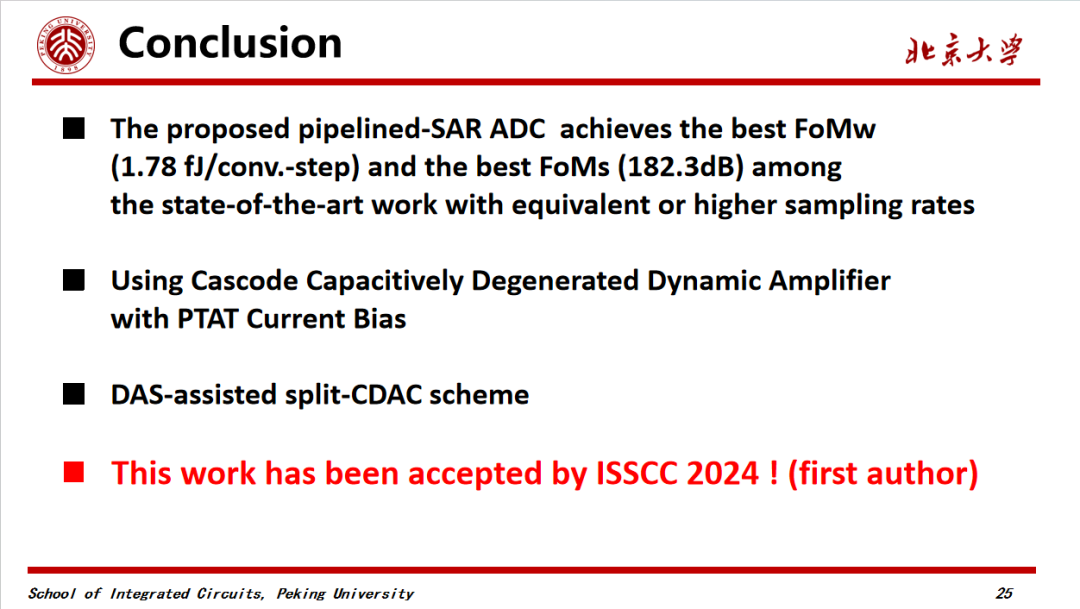

同一周内,第71届国际固态电路大会(ISSCC 2024)公布了录取论文和会议议程,2003网站太阳集团首页欢迎您2020级本科生陈卓毅作为第一作者的论文A 182.3dB FoMs 50MS/s Pipelined-SAR ADC using Cascode Capacitively Degenerated Dynamic Amplifier and MSB Pre-Conversion Technique(《一个182.3dB FoMs的使用了容性源极负反馈的共源共栅动态放大器和最高位提前转换技术的流水线-逐次逼近型模数转换器》)被录用,论文的通讯作者是集成电路学院的沈林晓老师和叶乐老师。

陈卓毅的论文正式通过评审的邮件

模数转换器(ADC)是连接模拟世界和数字世界的关键接口,在混合信号集成电路系统中有着重要作用。流水线-逐次逼近型模数转换器(pipelined-SAR ADC)是较为常用的具有较高能效的模数转换器。级间余量放大器是该模型中的一个重要模块,其它需要高增益和高线性度,这通常是由闭环放大器实现的,但是由于现有的闭环放大器能耗较大,使其成为整个ADC系统的能效瓶颈。

针对这个难点的一条技术路线是近年提出的开环动态放大器。它具有很高的能效,但因为线性度差、增益低、输出摆幅小等问题,极大地限制了其应用场景。对此,陈卓毅提出了共源共栅的容性源极负反馈的动态放大器和最高位提前转换技术,显著提高了线性度和增益,同时采用温度补偿的电流偏置方案提升PVT涨落下的性能鲁棒性。依托以上技术,芯片样片在奈奎斯特频率的输入下达到目前在相同或更高采样率的模数转换器中能效的世界纪录。

陈卓毅的科研工作始于一篇文献的学习。从大二开始,他在沈老师的课题组组会中旁听学习。一次,老师给陈卓毅一篇有关数模转换器放大器的文献进行学习,在对文献中放大器结构进行复现时的过程中,他对放大器增益不够、性能不佳的的问题产生了浓厚的兴趣。有什么方法可以解决这些问题,提高放大器的性能呢?陈卓毅开始着手对这个问题开展了研究。

在前人工作的基础上,他对已有的电路结构进行优化,将芯片设计好的方案交给厂家生产芯片,随后对芯片的性能进行测试测试芯片的性能,并和已有的芯片的性能进行对比。陈卓毅兴奋地发现,自己优化过后的模数转换器的能效竟然达到了前所未有的高度!

陈卓毅在工作中

陈卓毅在本科生科研项目答辩中总结论文成果的PPT

陈卓毅的项目需要把设计方案交给厂家生产芯片,然后对芯片进行性能测定。但是在给公司交付方案最后期限的前几天,他在某次仿真模拟时突然发现了设计中的重要漏洞,整个程序几乎无法正常运行。这时设计版图已经接近完成,来不及重新返工。他焦急万分,仔细分析了很久都没能有找到出现漏洞的原因。在巨大的压力下,陈卓毅几近崩溃,眼看着大半年的努力在此刻仿佛就要付诸东流。在火烧眉毛的紧急关头,他找到了实验室的师兄帮他进行分析。师兄安慰他平稳心态,帮助他规划修复的步骤,在短短几天里极限操作,赶在截止期限前弥补了漏洞,方案终于得以如期交付。

面对自己取得的成绩,陈卓毅始终保持着谦逊的态度:

“我只是在实际应用上提出了一个可能性。而正是因为有无数科研工作者们不断提出各种可能性,才有更多的优秀技术得以被真正应用。”

当陈卓毅在科研工作中遇到问题时,或者当事实和直观想象不符合时,他总是对其中的奥秘充满了好奇。这种好奇心激励着他不断钻研、不断探索,在科研的道路上阔步向前。未来,陈卓毅也将永葆对一切事物的好奇心,在北大继续博士阶段的学习。

陈卓毅在未名湖畔

信科学子

国际平台大放异彩

信科学子在国际平台上取得瞩目成就早已不是个例。2022年6月,时为北大2003网站太阳集团首页欢迎您2018级本科生郭资政在国际计算机学会(ACM)2022年度学生科研竞赛(SRC)中因芯片设计自动化(EDA)领域的工作获得了本科生组全球第一名。郭资政主要围绕着芯片设计自动化中的静态时序分析领域做了一系列创造性的工作。他首次提出了使用GPU加速静态时序分析的算法,克服了GPU这类并行计算硬件上处理不规则电路图数据的困难。此外,他在实现线性时空复杂度的路径分析算法的基础上,结合算法理论和硬件架构的相关知识,进一步提出了GPU并行编程模型下的路径分析方法,将效率提高了多个数量级。

郭资政还积极探索EDA和人工智能的交叉方向。同时他还探索将时序分析过程与神经网络训练进行类比,提出了学术界首个基于可微时序引擎的布局优化算法,极大提升了布局算法的性能。

郭资政在EDA设计精英挑战赛上

郭资政取得学生科研竞赛(SRC)本科生组全球第一名

北大学子在国际舞台上接连取得佳绩

不仅彰显了北大的科研实力

体现了新时代青年的青春力量

更展现了北大人在勇攀科研高峰

推动科学进步上的执着与追求

期望更多北大学子能够站上国际舞台

在全世界的聚光灯下发出北大声音