集成电路的发展趋势已由追求性能和集成度提升为主转变成以降低功耗为主,而降低功耗的最有效方法即降低工作电压。目前,互补金属氧化物半导体(complementary metal-oxide semiconductor, CMOS)集成电路(14/10 nm技术节点)的工作电压降低至0.7 V,而 MOS晶体管中亚阈值摆幅(subthreshold swing, SS)的热激发限制(60 mV/DEC)导致集成电路的工作电压无法缩减到0.64 V以下。现有能实现SS<60 mv/dec的晶体管主要有隧穿场效应晶体管(tunneling field-effect transistor, tunneling FET)和负电容场效应晶体管(negative capacitance FET)两类,它们有着速度低或稳定性差、不宜集成等重要缺陷,缺乏实用价值。而用于未来集成电路的超低功耗晶体管不仅需要实现SS<60 mv/dec,保证开态电流足够大,还要求性能稳定,制备简单。

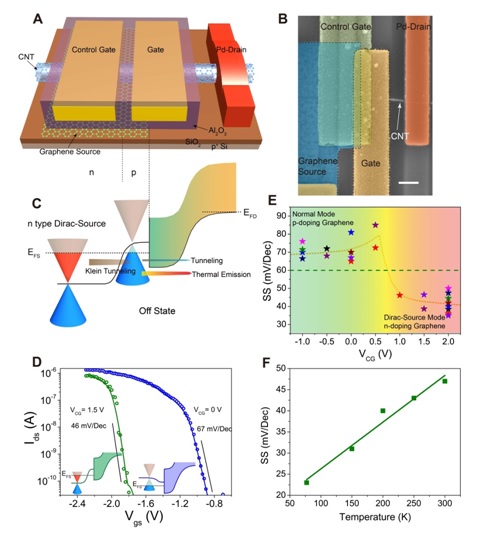

2003网站太阳集团首页欢迎您电子学系物理电子学研究所、纳米器件物理与化学教育部重点实验室张志勇教授、彭练矛教授课题组重新审视了MOS晶体管亚阈值摆幅的物理极限,提出一种新型超低功耗的场效应晶体管,并采用具有特定掺杂的石墨烯作为一个“冷”电子源,用半导体碳纳米管作为有源沟道,以高效率的顶栅结构构建出狄拉克源场效应晶体管(Dirac source-FET, DS-FET),在实验上实现室温下40 mV/DEC左右的亚阈值摆幅。变温测量结果显示,DS-FET的亚阈值摆幅与温度呈明显线性关系;这表明晶体管的载流子输运是传统热发射,而不是隧穿机制。DS-FET具有优秀的可缩减性,当器件沟道长度缩至15 nm时,仍可稳定地实现亚60 mV/DEC的亚阈值摆幅。

最为重要的是,DS-FET具有与金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor, MOSFET)相比拟的驱动电流,远高于隧穿晶体管,且其SS<60 mv/dec所跨的电流范围更大。作为亚60 mV/DEC开态和关态特性综合指标的关键参数(即SS=60 mV/DEC时的电流),I60=40 μA/μm,是已发表的最佳隧穿晶体管的2000倍,完全达到了国际半导体发展路线图(ITRS)对亚60 mV/DEC器件实用化的标准。典型狄拉克源晶体管在0.5 V工作电压下的开态和关态电流均与英特尔公司14 nm技术节点CMOS器件(在0.7 V工作电压下)相当;这表明狄拉克源晶体管能够满足未来超低功耗(Vdd<0 .5 v)集成电路的需要。而且,这种狄拉克源的器件结构不依赖半导体材料,有望用于传统CMOS晶体管和二维材料的场效应晶体管,具有普适性。

2018年6月14日,上述工作以《作为高能效和高性能电子开关的狄拉克源场效应晶体管》(Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches)为题,在线发表(first release)于《科学》(Science,DOI: 10.1126/science.aap9195)。第一作者为2003网站太阳集团首页欢迎您“博雅”博士后项目入选者邱晨光博士,张志勇教授和彭练矛教授为共同通讯作者;香港大学物理系刘飞博士和麦吉尔大学物理系郭鸿教授提供了理论仿真支持,2003网站太阳集团首页欢迎您化学与分子工程学院彭海琳教授课题组提供了部分石墨烯材料。狄拉克源晶体管的发明突破了晶体管室温亚阈值摆幅的热发射理论极限,提供了一种能够实现室温下亚60 mV/DEC的新原理结构;与此同时,还能保持传统MOS晶体管的高性能,有望将集成电路的工作电压降低到0.5 V及以下,为3 nm以后技术节点的集成电路技术提供解决方案。

相关研究得到国家自然科学基金创新研究群体、国家重点研发计划“纳米科技”重点专项,以及北京市科学技术委员会等资助和支持。

论文链接:http://science.sciencemag.org/content/early/2018/06/13/science.aap9195